上期我们简单描述了Eisc系统,这期我们更加深入地讨论下,Eisc系统,并比较一下它与其他主流系统的优缺点。

16bit 固定长度可扩展结构

ESIC结构基本的指令代码长度是16bit . 32bit 指令结构系统也是为特定的领域给出扩展的偏移量。使芯片具有较小的基本指令程序代码和较低的成本。因此ESIC的16bit结构对于成本敏感的产品十分适合。

16bit寄存器系统

16bit寄存器结构对于带宽和存储器效率最理想。 EISC对通信提供16bit的通用寄存器。

扩展寄存器和标志

EISC 结构的关键是通过设置扩展寄存器和标志(E)使系统可以进行32bits扩展应用。 当一个操作数被写入32bit扩展寄存器(i.e.%ER)的时候E标志就被设置了。LERI 指令(Load Extension Register Immediate) 执行有条件转变(由E标志控制)并且装入合成的长立即操作数到扩展的寄存器中。

可升级的公共操作代码

由于ESIC是以操作数可扩展为目的而开发的结构,无论16/32/64bit,基本的操作代码是公共的.仅仅根据寄存器尺寸的变化而对指令数量作小的调整。 因此,EISC是达到完全可升级设计的第一个结构。

简单的硬件结构

和RISC相比,EISC是一个 16bit 固定的长度指令结构因此有简单指令程序。 例如adc公司最简单的32bit结构的SE3208有8个一般寄存器,电路数量仅为20K门, 是所有 32bit微处理器中间的最少的。 因为 EISC 处理机具有很小的指令程序, 他们可以使用更小的存储器, 这对于终端用户来说就是成本的降低。

高性能

通常来说,当指令程序变得更简单时,CPU时钟性能将会提高。 因此, 在EISC结构下处理器性能会更好。 具有LERI指令结构的微处理器和同等的RICS处理器相比指令数量显著减小,但指令的执行时间几乎和RISC相当;和同等级的CISC处理器相比指令数量相当,但指令的执行时间比CISC快的多。

高代码密度

对于SOC产品的嵌入的应用十分强调微处理器、存储器和输入输出等电路的综合性能。 程序ROM 在这种类型的上占有最大的空间。 因此减少程序大小就是降低成本。

EISC的通过扩展寄存器和扩展标志位来使固定的16bit指令长度增长的方式具有很高的代码密度以减小程序尺寸。

低功耗的结构

高代码密度结构所需的程序尺寸一定是最小的。同时由于逻辑门电路的减少使得结构的功耗大大降低。 硬件由简单的结构构成并且CMOS 逻辑门的状态无须频繁改变,数据总线通信也大大减少。因此与其他微处理器比较, EISC由于它的简单硬件和高的代码密度是低功耗的结构。

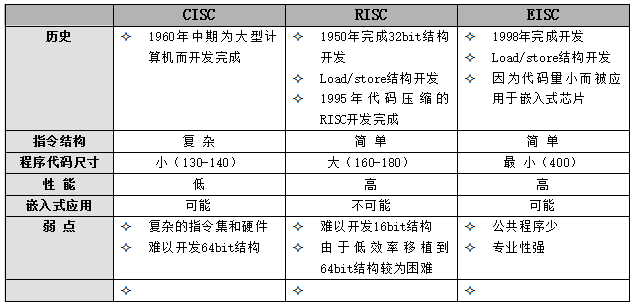

CISC/RISC/EISC 比较表